I circuiti sequenziali sono circuiti elettronici digitali in cui il valore della [delle] uscita [uscite] in un certo istante non dipende solo dal valore degli ingressi in quell'istante, ma anche dal valore assunto dagli ingressi precedentemente.

Esempi evoluti di circuiti sequenziali sono i registri e i contatori.

Sono dei circuiti con memoria, nel senso che conservano nello stato la situazione attuale.

In generale si puo' dire che nei circuiti sequenziali esiste un collegamento di reazione (feedback) che riporta nella rete combinatoria di ingresso lo stato delle uscite, attraverso un elemento di memoria.

Esistono due tipi fondamentali di circuiti sequenziali:

- sincroni (se c'è un comando esterno di sincronizzazione detto clock che gestisce quando gli ingressi devono essere letti e quando le uscite e lo stato interno possono cambiare)

- asincroni (se non c'è il clock a comandare la lettura degli ingressi e l'eventuale cambiamento dello stato interno e delle uscite).

Si definiscono quindi reti sequenziali sincrone quelle in cui lo stato interno e di conseguenza, eventualmente, l'uscita, variano solo se è presente un particolare impulso di sincronizzazione detto clock (CK).

L'elemento fondamentale ed elementare è la memoria ad un solo bit.

La cella di memoria elementare ad un solo bit si chiama Latch se asincrono e Flip-Flop (FF) se sincrono.

A volta si chiama il Latch anche Flip-Flop asincrono.

Il segnale di clock è caratterizzato da un'onda rettangolare in cui indichiamo con T1 la durata dell'impulso "alto" e con T2 la durata dell'impulso "basso", essendo poi T1+T2 = T la durata complessiva del periodo.

Si definisce duty cycle (d.c.) il rapporto tra T1 e T.

d.c.% = T1/T * 100.

L'onda quadra è caratterizzata da un d.c. del 50%.

Esistono due tipi fondamentali di circuiti sequenziali sincroni. Quelli comandati sul livello (o positivo o negativo) oppure quelli comandati sul fronte di salita (PET: Positive Edge Triggered) o sul fronte di discesa (NET: Negative Edge Triggered).

Latch SR

Il latch SR è un circuiti sequenziale asincrono che ha due ingressi chiamati S e R e due uscite Q e Q

Le uscite Q e Q devono essere sempre complementari, ossia se una è alta (1) l'altra deve essere (bassa) 0, e viceversa.

Il latch SR è caratterizzato dalla seguente tavola della verità:

| S | R | Q n | Qn | Spiegazione |

|---|---|---|---|---|

| 0 | 0 | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 0 | 1 | 0 | 1 | memorizza 0, reset |

| 1 | 0 | 1 | 0 | memorizza 1, set |

| 1 | 1 | n.a. | n.a. | non si può usare |

In pratica nel latch SR la combinazione S=0 e R=0 è quella che conserva i valori delle uscite e si mantiene memorizzato lo stato interno.

Porre R=1 con S=0 porta l'uscita Q a 0.

Porre invece S=1 con R=0 porta l'uscita Q a 1.

La configurazione del latch SR è tale che S=1 e R=1, contemporaneamente, non è ammessa perché renderebbe l'uscita indeterminata.

Nella tabella n a pedice indica l'istante ennesimo, mentre n-1 indica l'istante precedente.

Ecco lo schema logico con le 2 porte NOR:

E' possibile un analogo schema con due porte NAND.

A volte il latch SR può essere dotato di un segnale di abilitazione Enable (EN).

Si illustra nella figura lo schema a blocchi di un latch SR con abilitazione al livello alto.

Il latch SR con abilitazione è caratterizzato dalla seguente tavola della verità:

| EN | S | R | Q n | Qn | Spiegazione |

|---|---|---|---|---|---|

| 0 | X | X | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 0 | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 1 | 0 | 1 | memorizza 0, reset |

| 1 | 1 | 0 | 1 | 0 | memorizza 1, set |

| 1 | 1 | 1 | n.a. | n.a. | non si può usare |

In pratica quando EN=0 il latch è disabilitato e nulla può accadere né cambiare nello stato interno e nelle uscite, indipendentemente da quando valgono S e R che vengono indicati con X (don't care).

Se invece EN=1, il latch è abilitato e si comporta come un normale latch SR.

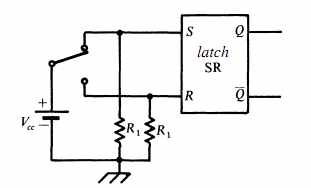

Circuiti Anti-rimbalzo

Una applicazione possibile per i latch SR è quella dei circuiti anti-rimbalzo (anti-bounce).

Gli interruttori e i deviatori meccanici possono essere causa di rimbalzi indesiderati che potrebbero essere causa di ulteriori problemi nei circuiti digitali collegati a valle.

Se si chiude un interruttore o un deviatore la lamina subisce un certo numero di oscillazioni, a causa della sua elasticità.

Se si usasse un semplice condensatore per fare un filtro passa basso si avrebbe una perdita della velocità nella risposta.

Se si usa invece il seguente collegamento si risolve meglio il problema dei rimbalzi:

Quando il deviatore è nella posizione S risulta S=1 e R = 0 per cui Q = 1.

Quando il deviatore si porta dalla posizione S alla R, in una prima fase la lamella del deviatore non tocca i punti S e R per cui S=0 e R = 0 e l'uscita conserva lo stato Q = l.

Nell'istante in cui la lamella tocca il punto R si ha: S=0 e R = 1.

L'uscita diventa: Q = 0 ; i piccoli rimbalzi meccanici fanno assumere agli ingressi i valori S=0 e R=0 e S=0 e R=1 che confermano Q = 0.

In definitiva l'uscita Q ha cambiato il suo stato logico ma senza rimbalzi.

Flip-Flop

I flip-flop si contraddistinguono dai latch per la presenza di un segnale di sincronizzazione (clock: CK). E' il segnale di Clock che stabilisce il momento in cui le uscite e lo stato interno possono eventualmente variare, se gli altri ingressi lo consentono.

Esistono due categorie:

- quelli comandati dalle transizioni del segnale di clock (o comandati sul "fronte"), detti anche edge triggered, in tal caso si parla di PET (positive edge triggered) oppure NET (negative edge triggered) se si considera la transizione dal basso all'alto (fronte di salita) oppure dall'altro al basso (fronte di discesa) rispettivamente.

- quelli comandati da un impulso, pulse triggered o master slave (lettura sul fronte di salita, modifica dell'uscita e dello stato interno sul fronte di discesa).

Esistono anche qui diversi tipi di Flip-Flop:

- tipo SR,

- tipo D,

- tipo JK,

- tipo T

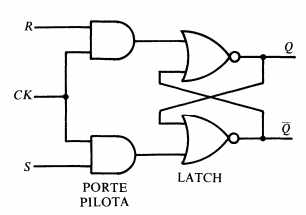

Flip-Flop tipo SR

Si distinguono dal latch SR per il loro funzionamento sincrono (ricordo che il latch è asincrono).

Ecco lo schema logico:

Il FF-SR è caratterizzato dalla seguente tavola della verità:

| CK | S | R | Q n | Qn | Spiegazione |

|---|---|---|---|---|---|

| 0 | X | X | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 0 | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 1 | 0 | 1 | memorizza 0, reset |

| 1 | 1 | 0 | 1 | 0 | memorizza 1, set |

| 1 | 1 | 1 | n.a. | n.a. | non si può usare |

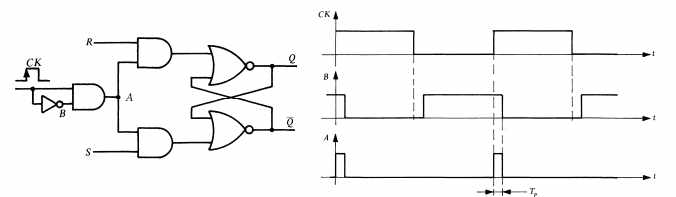

Questo FF è però sensibile al livello. Per renderlo sensibile ad un impulso più breve (ossia per renderlo, sostanzialmente, un PET), occorre complicare un po' il circuito e sfruttare il fatto che la porta NOT ha un tempo di ritardo di propagazione non nullo.

Come si vede dalla figura, il segnale A risulta essere il prodotto logico, attraverso la porta AND, del segnale di clock CK, e del segnale B (che è il clock ritardato di quanto vale il tempo di ritardo di propagazione della porta NOT). Il segnale A è dunque un segnale impulsivo, con un duty cycle piuttosto piccolo (sicuramente inferiore al 5%).

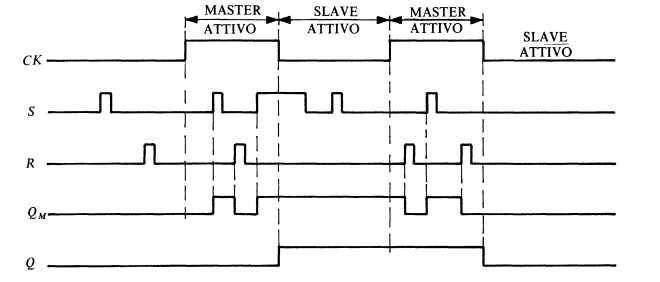

Flip-Flop tipo SR Master-Slave

Per avere un funzionamento Master-Slave si possono utilizzare due FF SR in cascata che vengono comandati dal CK e dal Clock negato da una porta NOT (CK).

Ecco lo schema a blocchi: .

.

Ecco la tabella della verità del circuito:

| CK | CK | S | R | Q n | Qn | Spiegazione |

|---|---|---|---|---|---|---|

| 0 | 1 | X | X | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 0 | 0 | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | 0 | 0 | 1 | 0 | 1 | memorizza 0, reset |

| 1 | 0 | 1 | 0 | 1 | 0 | memorizza 1, set |

| 1 | 0 | 1 | 1 | n.a. | n.a. | non si può usare |

In sostanza, quando CK = 0, il master è disabilitato, e lo slave è abilitato perché CK = 1. Ma l'uscita dello slave dipende allora dallo stato interno di memoria del master QM e QM che sono rispettivamente collegati a S e R per lo slave.

Invece quando CK = 1 il master è abilitato, a seconda del valore di S e R del master puo' cambiare lo stato interno del master e quindi QM e QM, ma non cambiano le uscite Q e Q dello slave, perché lo slave è disabilitato. Esse cambieranno - eventualmente - al successivo fronte di discesa di CK.

La situazione può essere illustrata dal seguente diagramma temporale: .

.

C'è comunque una differenza tra un FF Master-Slave e uno di tipo NET: entrambi commutano il valore dell'uscita, se occorre, al fronte di discesa del clock, ma nel caso MS i valori degli ingressi vengono invece letti al momento del fronte di salita. Si puo' dire che un MS legge sul fronte di salita e commuta sul fronte di discesa, se occorre che lo faccia.

Flip-Flop tipo SR con Preset e Clear

In alcuni casi può essere utile preassegnare il valore iniziale dello stato interno del flip-flop, con degli ingressi particolari.

Essi sono Preset (PR) che se abilitato porta l'uscita Q = 1 e Clear (CL) che se abilitato porta la stessa uscita Q a zero.

E' evidente che PR e CL non possono essere abilitati contemporaneamente, non avrebbe senso. .

.

Nella figura c'è lo schema a blocchi di un FF di tipo NET, con ingressi di PR e CL abilitati sul livello basso.

Quindi PR=0 porta Q=1; CL=0 porta Q=0.

E' dunque evidente che non può essere PR=0 e CL=0 contemporaneamente.

Per funzionare, dopo la preassegnazione iniziale, PR e CL devono essere entrambi disabilitati.

Flip-Flop tipo JK

E' un Flip-Flop con due ingressi, chiamati J e K che si differenzia da quello SR non tanto per il nome degli ingressi, quanto per il fatto che l'ultima riga della tavola della verità non è proibita come accadeva nell'SR ma ha la funzione di Toggle, ossia fa' commutare lo stato interno e l'uscita. La differenza che se J = K = 1, l'uscita Q cambia stato. In tal modo viene eliminata l'indeterminazione che si ha in un SR quando si pone S = R = 1.

Ecco lo schema logico:

La figura indica lo schema a blocchi di un FF-JK di tipo PET (Positive edge triggered). Si possono fare anche gli analoghi casi di FF-JK NET (Negative Edge Triggered) e di tipo MS (Master Slave).

Il FF-JK è caratterizzato dalla seguente tavola della verità:

Come si vede nella tabella, se il clock è basso gli ingressi J e K non contano e l'uscita Qn+1= Qn. Vuole dire che l'uscita successiva sarà uguale a quella precedente (non cambia).

Invece l'uscita potrà cambiare solo se il clock si trova nel fronte di salita.

Anche se il clock è nel fronte di salita, l'uscita non cambia se J = 0 e K = 0.

Se il clock è nel fronte di salita, se J = 0 e K = 1 si ha Qn+1= 0 (condizione di reset).

Invece se il clock è nel fronte di salita, se J = 1 e K = 0 si ha Qn+1= 1 (condizione di set).

La novità è la condizione di Toggle che si ha se il clock è nel fronte di salita, se J = 1 e K = 1: in questo caso accade che Qn+1= Qn.

Il FF-JK è un flip-flop universale, nel senso che attraverso di esso si possono ottenere anche il tipo D e il tipo T (che vedremo fra poco), e dunque sia i registri, sia i contatori, sia qualsiasi circuito sequenziale.

Nei seguenti diagrammi temporali è illustrato in dettaglio il comportamento dei tre tipi di FF-JK.

Flip-Flop tipo D

Il flip-flop D è un flip-flop con un solo ingresso D (Dato) e due uscite complementari Q e Q.

L'uscita Q assume lo stesso stato logico dell'ingresso D dopo che si è applicato il segnale di Clock CK.

Ecco lo schema a blocchi:

Ecco la tavola della verità:

| CK | D | Q n | Qn | Spiegazione |

|---|---|---|---|---|

| 0 | X | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 0 | 0 | 1 | memorizza 0 |

| 1 | 1 | 0 | memorizza 1 |

Il FF-D puo' essere realizzato con un FF-JK mettendo K=J attraverso l'uso di una porta NOT.

e principalmente viene utilizzato nei registri.

Flip-Flop tipo T

Il flip-flop T è un flip-flop con un solo ingresso T (Toggle) e due uscite complementari Q e Q.

L'uscita Q assume lo stesso stato logico opposto a quello che aveva precedentemente se l'ingresso T è abilitato dopo che si è applicato il segnale di Clock CK.

Ecco lo schema a blocchi:

Ecco la tavola della verità:

| CK | T | Q n | Qn | Spiegazione |

|---|---|---|---|---|

| 0 | X | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 0 | Qn-1 | Qn-1 | conserva lo stato, memoria |

| 1 | Qn-1 | Qn-1 | toggle |

Il FF-T puo' essere realizzato con un FF-JK mettendo K=J attraverso il collegamento diretto con un "filo" di J e K.

e principalmente viene utilizzato nei contatori.